- A+

振动、温度、压力和光等现实世界的信号需要精确的信号调理和信号转换,然后才能在数字域中进行进一步数据处理。为了克服当前高精度应用的多种挑战,需要一个精心设计的低噪声模拟前端来实现最佳信噪比(SNR)。许多系统既负担不起最昂贵的器件,也无法承受低噪声器件的更高功耗。本文提出了一种系统的方法来设计一个增益模块和ADC组合,并给出一个支持此方法的实例。在调理低频(接近dc)信号时,该电路进行噪声计算和分析。

设计模拟前端时,请遵循以下七个步骤:1) 描述传感器或增益模块前部的电气输出;2) 计算ADC的需求;3) 为信号转换找到最佳ADC + 基准电压;4) 为运算放大器找到最大增益并定义搜索条件;5) 找到最佳放大器并设计增益模块;6) 根据设计目标检查解决方案总噪声;7) 运行模拟并验证。

第1步:描述传感器或增益模块前部的电气输出

信号可能直接来源于传感器,也可能在到达增益模块之前经过EMI和RFI滤波器。为了设计增益模块,必须知道信号的ac和dc特性以及可用的电源。知道了信号的特性和噪声电平后,我们就能知道选择ADC时需要何种输入电压范围和噪声电平。假设有一个传感器,以250 mV p-p(88.2 mV rms)和25 μV p-p噪声的满量程幅度输出一个10kHz信号。我们进一步假设系统中有一个可用的5V电源。有了这些信息,我们应该能计算出第2步中的ADC输入端的信噪比。为简化数据处理和避免混淆,假设我们将该解决方案设计为在室温下工作。

第2步:计算ADC的需求

我们需要何种ADC、采样速率如何、多少位、噪声指标如何?若从第一步知道了输入信号幅度以及噪声信息,我们就能计算出增益模块输入端的信噪比(SNR)。我们需要选择一个有更佳信噪比的ADC。在选择ADC时,知道SNR将有助于我们计算有效位数(ENOB)。

理想的ADC数据手册总会标出SNR和ENOB。此例中所需要的86.8 dB SNR和14.2位ENOB决定了我们应选择一个16位的模数转换器。此外,奈奎斯特准则要求采样率(fs)应至少两倍于最大输入频率(fin),因此一个20-kSPS ADC应该就已足够。下一步我们需要设计总体解决方案,使得噪声密度不超过416 nV/rt-Hz。

第3步:为信号转换找到最佳ADC+基准电压

有了一系列的搜索条件,我们就有许多种方法找到合适的ADC。要找到一个16位ADC,最简单的方法之一就是使用厂商网站上的搜索工具。输入分辨率与采样速率,就可找到许多推荐的ADC。

许多16位的ADC满足14.5位ENOB需求。如果您想得到更佳的噪声性能,可使用过采样迫使ENOB达到16位(由4^n过采样得到n位增强)。通过过采样,您可以使用较低分辨率的ADC:256过采样的12位ADC(4^4过采样)可得到16位噪声性能。在我们的例子中,这意味着5.126 MHz采样率的12位ADC(20 kSPS × 256),或是4^2过采样的14位ADC;若1.28 MSPS则更佳。然而这些选择的成本却和AD7685(16位、250 kSPS ADC)相当。

AD7685参考输入具有动态输入阻抗,因此需进行去耦以使寄生电感最小(方法是在引脚附近放置一个陶瓷去耦电容,并用较宽的低阻抗走线进行连接)。一个22 μF陶瓷芯片电容可提供最佳性能。

第4步:为运算放大器找到最大增益并定义搜索条件

有了ADC的输入电压范围将有助于我们设计增益模块。为了最大化动态范围,我们需要在给定的输入信号和ADC输入范围内选取尽可能高的增益。这意味着我们可以将该例子中的增益模块设计成具有10倍的增益。

虽然AD7685很容易驱动,但驱动放大器需要满足某些要求。例如,为保持AD7685的SNR和转换噪声性能,驱动放大器产生的噪声必须尽可能低,但要注意增益模块可同时放大信号和噪声。若要使得噪声在增益模块前后都保持不变,我们需要选择具有更低噪声值的放大器和相关元件。此外,驱动器的THD性能应与AD7685相当,并且必须使ADC电容阵列以16位水平(0.0015%)建立满量程阶跃。来自放大器的噪声可使用外部滤波器进一步过滤。

运算放大器的输入端允许多大的噪声?牢记我们设计的总体解决方案的噪声密度不超过416 nV/rt-Hz。我们设计的增益模块应具有更低的本底噪声,系数为10,因为我们的增益为10。这将确保来自放大器的噪声远低于传感器的本底噪声。计算噪声裕量时,我们可假设运算放大器输入端的噪声大致等于运算放大器的总噪声加上ADC的噪声。

第5步:找到最佳放大器并设计增益模块

知道了输入信号带宽后,运算放大器选型的第一步是选择一个具有合理的增益带宽积(GBWP)的运算放大器(GBWP),并且该放大器可以最小的直流和交流误差处理该信号。为得到最佳的增益带宽积,需要知道信号带宽、噪声增益以及增益误差。下文给出这些术语的定义。一般而言,若想保持增益误差小于0.1%,推荐选用增益带宽比输入信号带宽大100倍的放大器。另外,我们需要一个可快速建立且驱动能力良好的放大器。注意,我们的噪声预算要求运算放大器输入端的总噪声低于40.8 nV/rt-Hz,而ADC规定的指标为7.9-nV/rt-Hz。总结运算放大器的查找条件如下:UGBW>1MHz、5-V单电源、良好的电压噪声、电流噪声、THD特性、低直流误差(不降低ADC性能)。

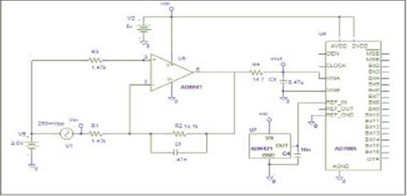

搜索ADC时采用相似的查找方法,本例我们选出AD8641。AD8641为低功耗、精密JFET输入放大器,具有极低的输入偏置电流和轨到轨输出特性,可在5 V至26 V电源下工作。相关数据在下表中列出。我们可采用表中的元件值对运算放大器进行同相配置。

所有有源和无源元件都各自产生噪声,因此选择不降低性能的元件尤其重要。例如,购买一个低噪声运算放大器并在其周围放置大电阻就是一种浪费。牢记一个1 kohm的电阻器可产生4 nV的噪声。

完整的解决方案

第6步:根据设计目标检查解决方案总噪声

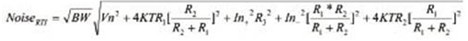

充分了解所设计电路中的各种误差源是极其重要的。为了获得最佳SNR,我们需要写出前述方案的总噪声方程。

方程公式1

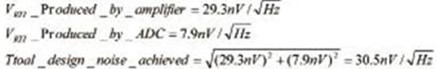

我们可算出运算放大器输入端的总噪声,并确保其低于41.6 nV/rtHz,一如我们所预期的那样。

方程公式2

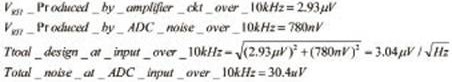

为了在整个带宽上对总噪声进行积分,我们可看到在滤波器带宽上的ADC输入端的总噪声是3.05μV,低于设计所需的4.16μV。由于AD8641的转折频率低于100 Hz,故此例中的低频噪声(1/f)可忽略不计。

方程公式3

保持良好的信噪比需要关注信号路径中每一处细节的噪声,并有良好的PCB布局。避免在任何ADC下方布设数字线路,否则会将噪声耦合至芯片管芯,除非在ADC下方铺一个接地层用作屏蔽。诸如CNV或时钟之类的快速开关信号不应靠近模拟信号路径。应避免数字信号与模拟信号交叠。

第7步:运行模拟并验证

刚开始验证电路设计时,使用Pspice宏模型(可从ADI网站下载)比较合适。快速模拟显示出我们为解决方案所设计的信号带宽。图5显示了位于AD7685输入端可选RC滤波器之前和之后的响应。

如图6所示,10-kHz带宽上的总输出噪声接近31μV rms,略低于41μV rms的设计目标。在量产之前需要制作原型并验证整套解决方案。

总结:如今许多设计要求低功耗、低成本,而许多系统既负担不起最昂贵的器件,也无法承受低噪声器件的更高功耗。为了从信号调理电路得到最低的本底噪声和最佳性能,设计者必须了解元件级别的噪声源。保持良好的信噪比需要关注信号路径每一处细节的噪声。通过遵循以上步骤,便可成功调理小型模拟信号,并使用超高分辨率ADC将其转换。