- A+

要:在高速数字电路设计过程中,工程师采取了各种措施来解决信号完整性问题,利用差分线传输高速数字信号的方法就是其中之一。在PCB中的差分线是耦合带状线或耦合微带线,信号在上面传输时是奇模传输方式,因此差分信号具有抗干扰性强,易匹配等优点。随着人们对数字电路的信息传输速率要求的提高,信号的差分传输方式必将得到越来越广泛的应用。

1 用差分线传输数字信号

如何在高速系统设计中考虑信号完整性的因素,并采取有效的控制措施,已成为当今国内外系统设计工程师和PCB设计业界的一个热门课题。利用差分线传输数字信号就是高速数字电路中控制破坏信号完整性因素的一项有效措施。

在印刷电路板上的差分线,等效于工作在准TEM模的差分的微波集成传输线对,其中,位于PCB顶层或底层的差分线等效于耦合微带线;位于多层PCB的内层的差分线,正负两路信号在同一层的,等效于侧边耦合带状线,正负两路在相邻层的,等效于宽边耦合带状线。数字信号在差分线上传输时是奇模传输方式,即正负两路信号的相位相差180°,而噪声以共模的方式在一对差分线上耦合出现,在接受器中正负两路的电压(或电流)相减,从而可以获得信号,消除共模噪声。而差分线对的低压幅或电流驱动输出实现了高速集成功耗的要求。

2 差分线的阻抗匹配

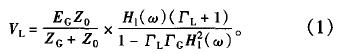

差分线是分布参数系统,因此在设计PCB时必须进行阻抗匹配,否则信号将会在阻抗不连续的地方发生反射,信号反射在数字波形上主要表现为上冲、下冲和振铃现象。式(1)是一个信号的上升沿(幅度为EG)从驱动端经过差分传输线到接收端的频率响应:

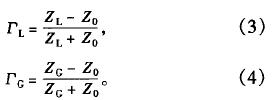

其中信号源的电动势为EG,内阻抗为:ZG,负载阻抗为ZL;Hl(ω)为传输线的系统函数;ΓL和ΓG分别是信号接收端和信号驱动端的反射系数,由以下两式表示:

由式(1)可以看出,传输线上的电压是由从信号源向负载传输的入射波和从负载向信号源传输的反射波的叠加。只要我们通过阻抗匹配使ΓL和ΓG等于0,就可以消除信号反射现象。在实际工程应用中,一般只要求ΓL=0,这是因为只要接收端不发生信号反射,就不会有信号反射回源端并发生源端反射。

由式(3)可知,如果ΓL =0,则必须ZL=Z0,即传输线的特性阻抗等于终端负载的电阻值。传输线的特性阻抗可以由有关软件计算出来,它和差分线的线宽、线距及相邻介质的介电常数有关,一般把差分线的特性阻抗控制在100Ω左右。值得注意的是,一个差分信号在多层PCB的不同层传输时(特别是内外层都走线时),要及时调整线宽线距来补偿因为介质的介电常数变化带来的特性阻抗变化。终端负载电阻的控制要根据不同的逻辑电平接口,来选择适当的电阻网络和负载并联,以达到阻抗匹配的目的。

3 差分线的端接

差分线的端接要满足2方面的要求:逻辑电平的工艺要求和传输线阻抗匹配的要求。因此,不同的逻辑电平工艺要采用不同的端接。本文主要介绍2种常见的适于高速数传的电平的端接方法:

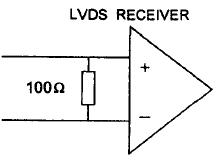

①LVDS电平信号的端接。

LVDS是一种低摆幅的差分信号技术,它上面的信号可以以几百Mbps的速率传输。LVDS信号的驱动器由1个驱动差分线的电流源组成,通常电流为3.5 mA。它的端接电阻一般只要跨接在正负两路信号的中间就可以了,如图1所示。

LVDS信号的接受器一般具有很高的输入阻抗,因此驱动器输出的电流大部分都流过了100Ω的匹配电阻,并产生了350 mV的电压。有时为了增加抗噪声性能,差分线的正负两路信号之间用2个5OΩ的电阻串联,并在电阻中间加1个滤波电容到地,这样可以减少高频噪声。随着微电子技术的发展,很多器件生产商已经可以把LVDS电平信号的终端电阻做到器件内部,以减少PCB设计者的工作。

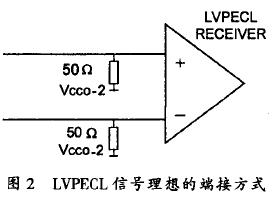

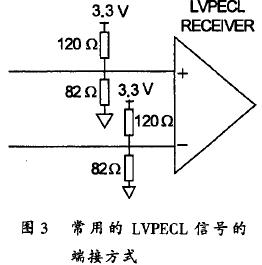

②LVPECL电平信号的端接。

LVPECL电平信号也是适合高速传输的差分信号电平之一,最快可以让信号以1 GBaud波特的速率传输。它的每一单路信号都有一个比信号驱动电压小2 V的直流电位,因此应用终端匹配时不能在正负两条差分线之间跨接电阻(如果在差分线之间跨接电阻,电阻中间相当于虚地,直流电位将变成零),而只能将每一路进行单端匹配。

对LEPECL信号进行单端匹配,要符合2个条件,即信号的直流电位要为1.3 v(设驱动电压为3.3 V,减2后,为1.3 V)和信号的负载要等于信号线的特性阻抗(50Ω)。因此可以应用以下理想的端接方式:

在实际的工程设计中,增加一个电源就意味着增加了新的干扰源,也会增加布线空间(电源的滤波网络要使用大量的布线空间),改变电源分割层的布局。因此在设计系统时,可以利用交直流等效的方法,对图2中的端接方式进行了等效改变。

在图3中,对交流信号而言,相当于120Ω电阻和82Ω电阻并联,经计算为48.7Ω;对于直流信号,两个电阻分压,信号的直流电位为:3.3×82/(120+82)= 1.34 V。因此等效结果在工程应用的误差允许范围内。

4 差分线的一些设计规则

在做PCB板的实际工作中,应用差分线可以很大程度上提高信号线的抗干扰性,要想设计出满足信号完整性要求的差分线,除了要使负载和信号线的阻抗相匹配外,还要在设计中尽量避免阻抗不匹配的环节出现。现根据实际工作经验,总结出以下规则:

- 差分线离开器件引脚后,要尽量相互靠近,以确保耦合到信号线的噪声为共模噪声。一般使用FR4介质时,50 Ω布线规则(差分线阻抗为100Ω)时,差分线之间的距离要小于0.2 mm;

- 信号线的长度应匹配,不然会引起信号扭曲,引起电磁辐射;

- 不要仅仅依赖软件的自动布线功能,要仔细修改以实现差分线的阻抗匹配和隔离;

- 尽量减少使用过孔和其他一些引起阻抗不连续的因素;

- 不要使用90°走线,可用圆弧或45°折线代替;

- 信号线在不同的信号层时,要注意调整差分线的线宽和线距,避免因介质条件改变引起的阻抗不连续。

5 结束语

在高速数字PCB设计中,运用差分线传输高速信号,一方面在对PCB系统的信号完整性和低功耗等方面大有裨益,另一方面也给的PCB设计水平提出了更高要求。作为设计者应该深刻理解传输线理论的有关概念,仔细分析出各种畸变现象的原因,找出合理有效的解决办法;还要不断把工作中积累的一些经验加以总结,并上升为理性认识,才能够取得满意的设计效果。

参考文献

[1] 廖承恩.微波技术基础[M].西安:西安电子科技大学出版社.1994.

[2] 霍华德约翰逊.高速数字设计[M].沈立译.北京:电子工业出版社,2004.

[3] 王先富,牛忠霞.微波宽带放大器的设计与EDA仿真[J].无线电通信技术,2005,31(1):51—53.